# Introduction to the IBIS Macro Model Library

## Arpad Muranyi Signal Integrity Engineering

**February 9, 2006**

### **Contents of the library**

- Three resistors

- R, VCR, CCR

- Three capacitors

- C, VCC, CCC

- Four inductors

- L, VCL, CCL, K

- 22 voltage and 22 current sources, including

- Delay, Min, Max, Abs, Sum, Mult, Div, PWL

- An ideal T-line

- Eight IBIS buffers

- Input, Output, IO, 3-state, Opensource,

IO\_opensource, Opensink, IO\_opensink

### Philosophy of examples

- Assumption:

- HSPICE with Verilog-A option installed, and/or

- SMASH installed (for the VHDL-A(MS) examples)

- All examples are ready to go

- No editing is necessary, just simulate and look at the waveforms

- The examples are simple, just enough to show the concept

- No attempt was made to show all possibilities

- The data files contain very short data tables so the waveforms may not all be smooth and rounded

- Some lines are commented out in the VHDL-A(MS) building blocks to allow them work in the evaluation version of SMASH (Seduction)

- A PERL script has been developed to extract and reformat the data from IBIS files so that the library building blocks can read it

#### **Test suite architecture**

#### Top level SPICE files

- Include the simulation control statements

- Contain simple stimulus source(s), load(s) and a call to the macro model netlist (i.e. template)

- Equivalent of the SI simulator tool's IBIS environment with an IBIS file using an [External Model] or [External Circuit] statement

- "Macro model template"-s

- Contain Verilog-A(MS) or VHDL-A(MS) netlists to instantiate the building blocks from the library

- Show how to pass parameter values into the instances

- Equivalent of a "complicated buffer's" macro model

- Model library file

- Contains the various building blocks of "primitives"

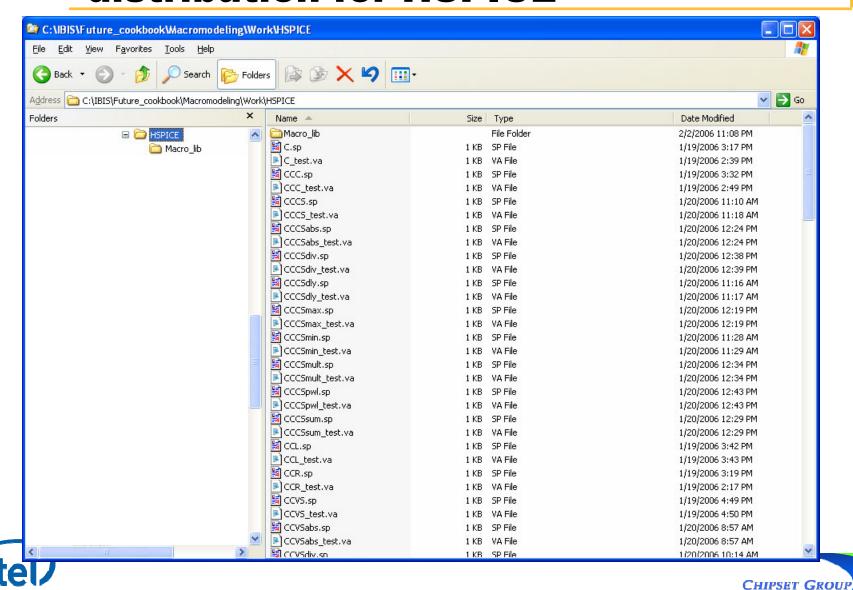

## File system of the Verilog-A(MS) distribution for HSPICE

- Installation directory of your choice

- One .sp and .va file per library building block

- The .sp file contains the simulation control and stimulus statements and the call to the .va netlist (or the "template" file)

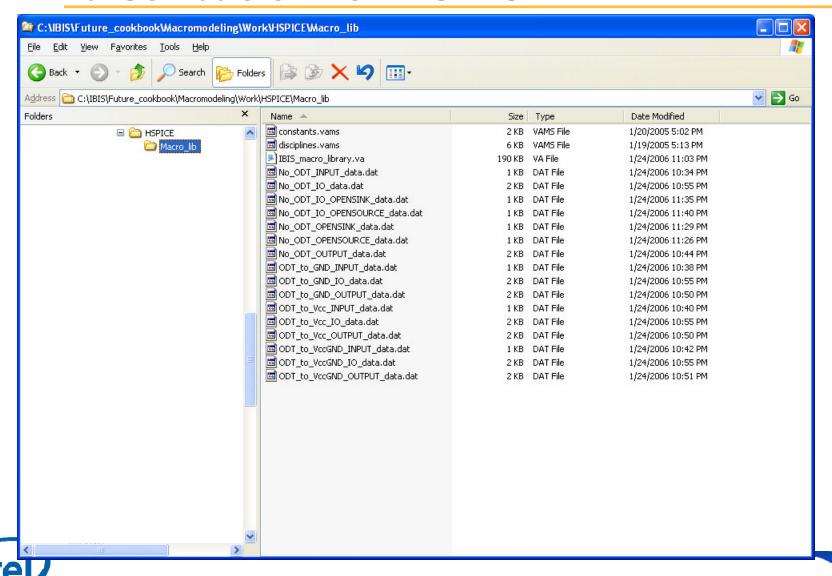

- Macro\_lib subdirectory

- Contains two mandatory files and the library file

- constants.vams

- disciplines.vams

- IBIS\_macro\_library.va

- plus a small collection of parameter data files (\*.dat)

- these files contain IBIS buffer parameters, such as C\_comp, I-V and V-t tables, or

- appropriate data tables for the PWL sources

### File system of the Verilog-A(MS) distribution for HSPICE

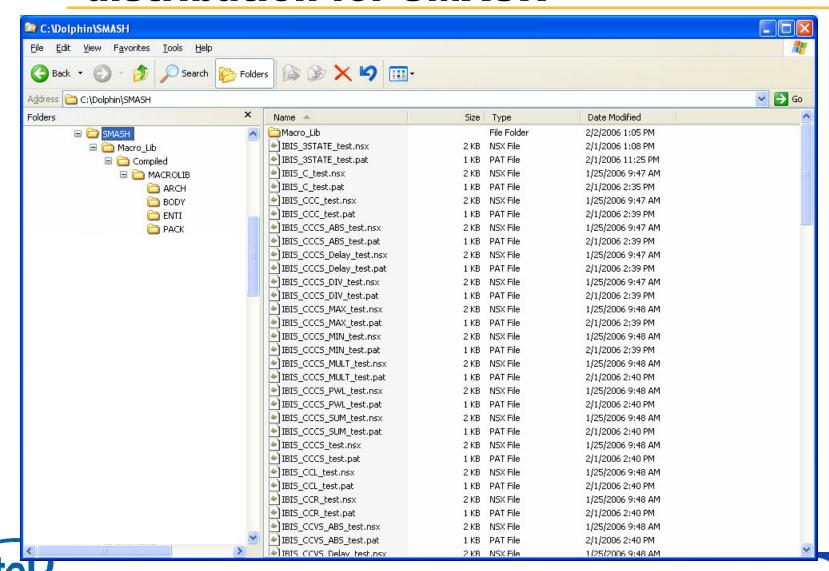

## File system of the Verilog-A(MS) distribution for HSPICE

CHIPSET GROUP

- Installation directory of your choice

- One .nsx and .pat file per library building block

- The .pat (pattern) file contains the simulation control statements

- The .nsx file contains both the top level SPICE and the VHDL-AMS netlist of the "template"

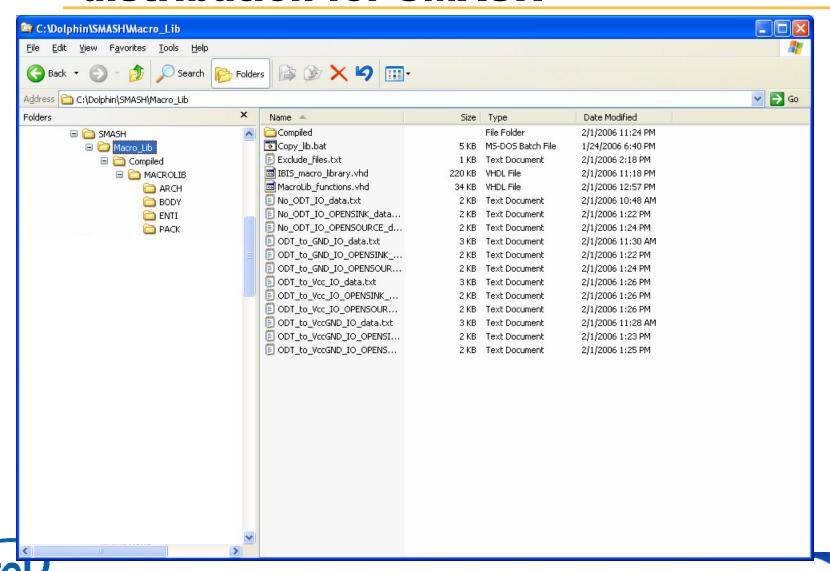

- Macro\_lib subdirectory

- Contains the library and a function file

- IBIS\_macro\_library.vhd

- MacroLib\_functions.vhd

- plus a collection of parameter data files (\*.txt)

- these files contain IBIS buffer parameters, such as C\_comp, I-V and V-t tables, or

- appropriate data tables for the PWL sources

CHIPSET GROUP

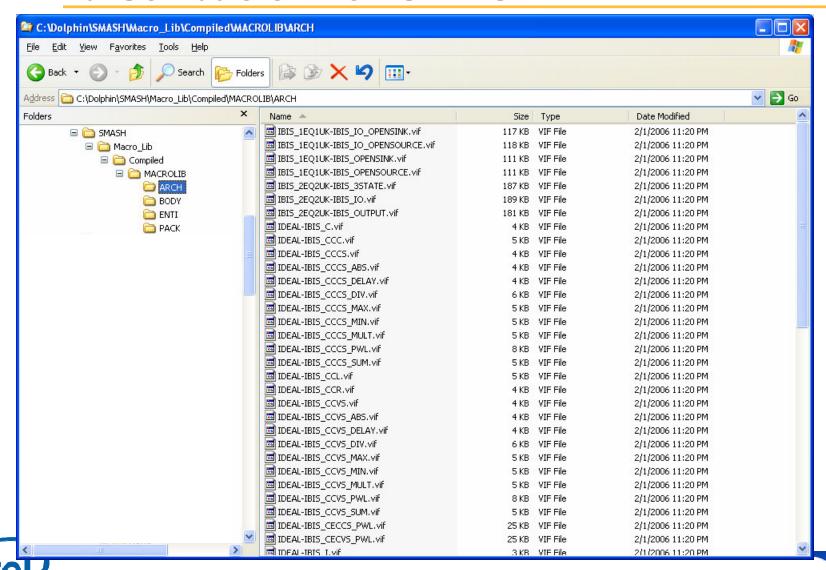

### The "Compiled" subdirectory

- The Macro\_lib directory of the VHDL-A(MS) distribution includes a directory called "Compiled"

- This contains a compiled version of the library and all of its functions as a convenience to speed up testing

- You don't have to use it, but it can save you time

- The "Copy\_lib.bat" file copy the compilation into the work area of each library building block example

- (Copying is faster than compiling it 63 times)

- The "Exclude\_files.txt" file will prevent the duplication of files which do not need to be copied

- This is a SMASH specific step, other tools may deal with the WORK and user library hierarchy in a different manner

CHIPSET GROUP

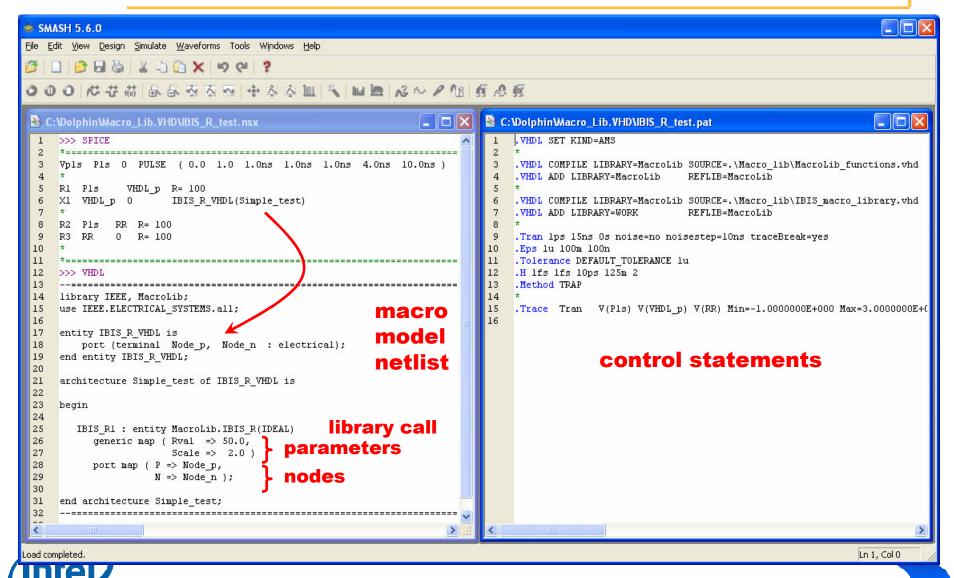

#### The resistor example - code

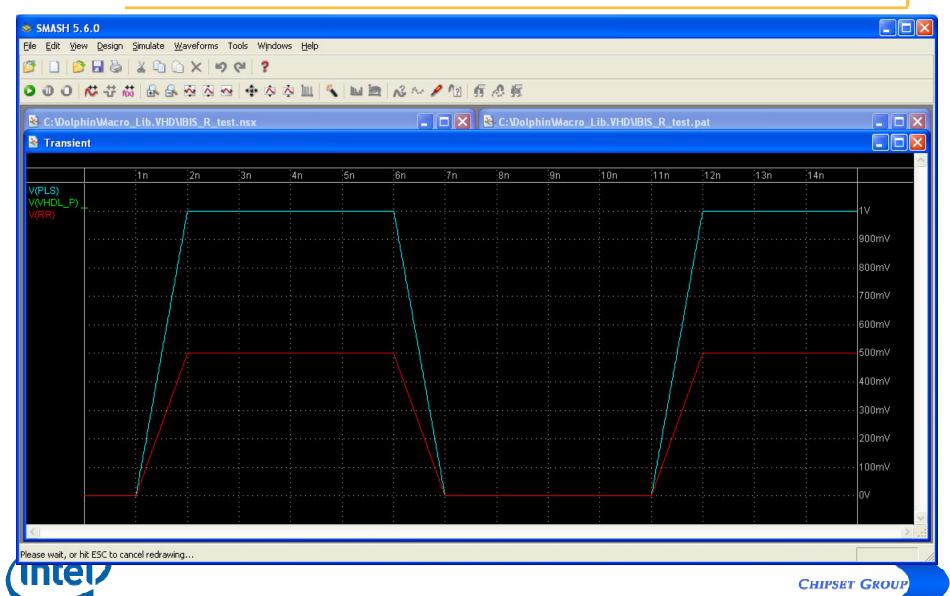

#### The resistor example - waveforms

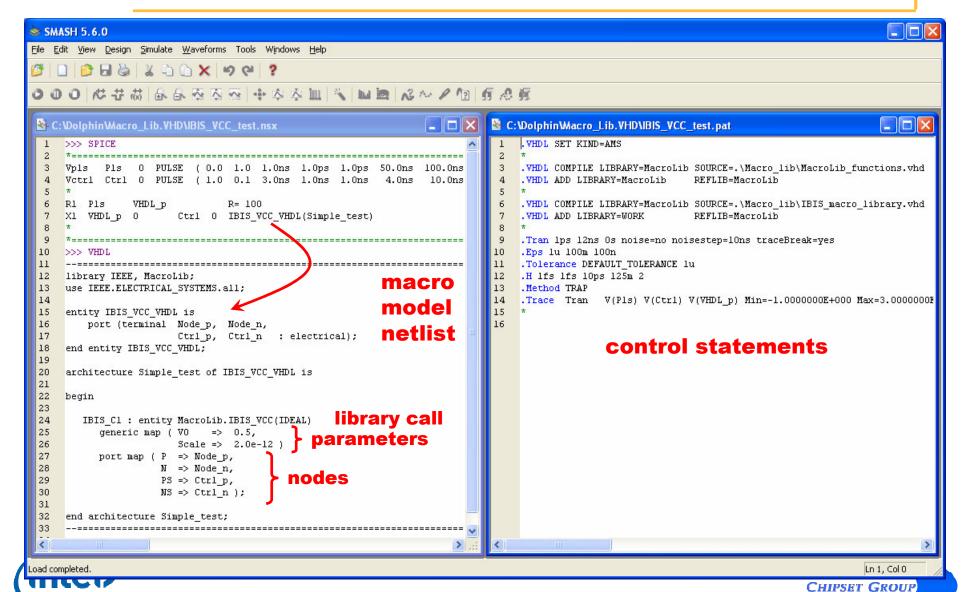

#### The VCC example - code

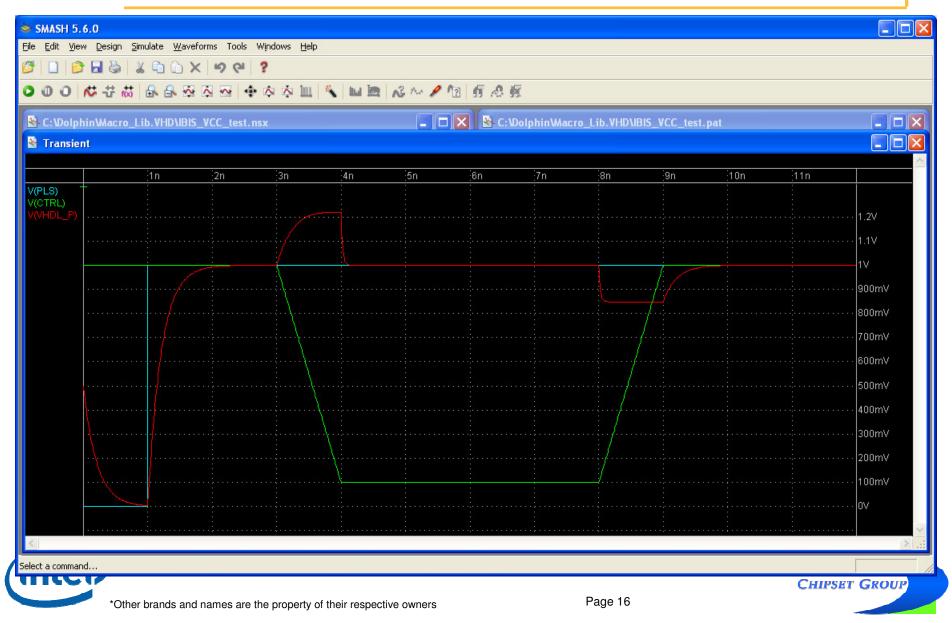

#### The VCC example - waveforms

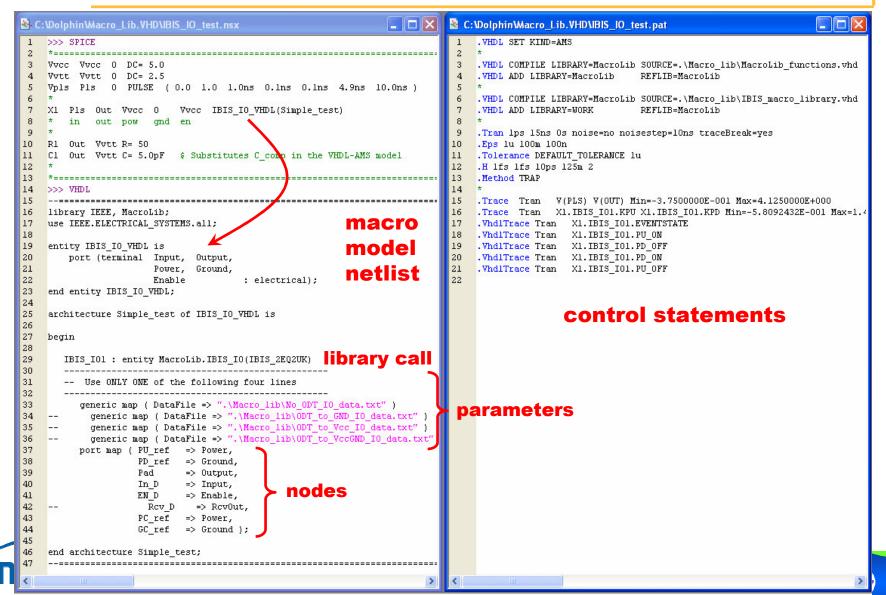

#### IBIS\_IO buffer example - code

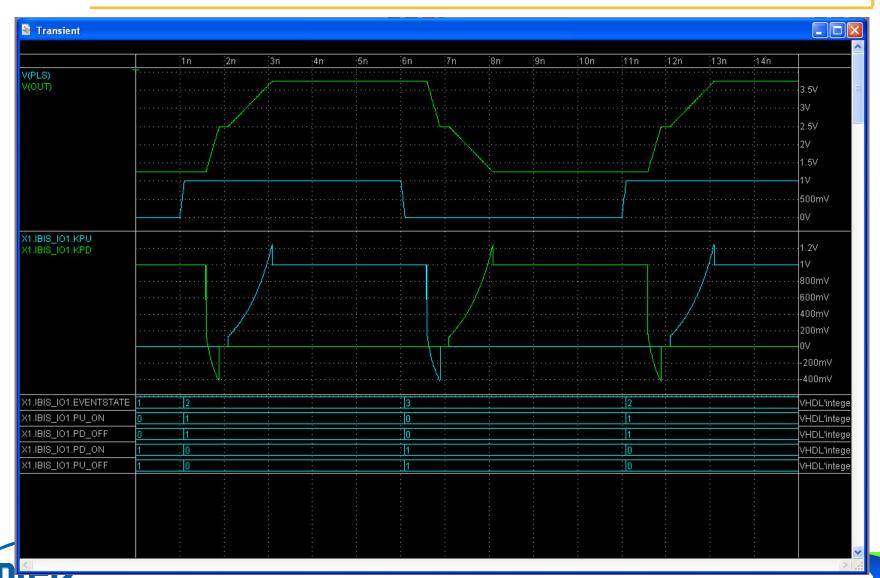

#### IBIS\_IO buffer example - waveforms

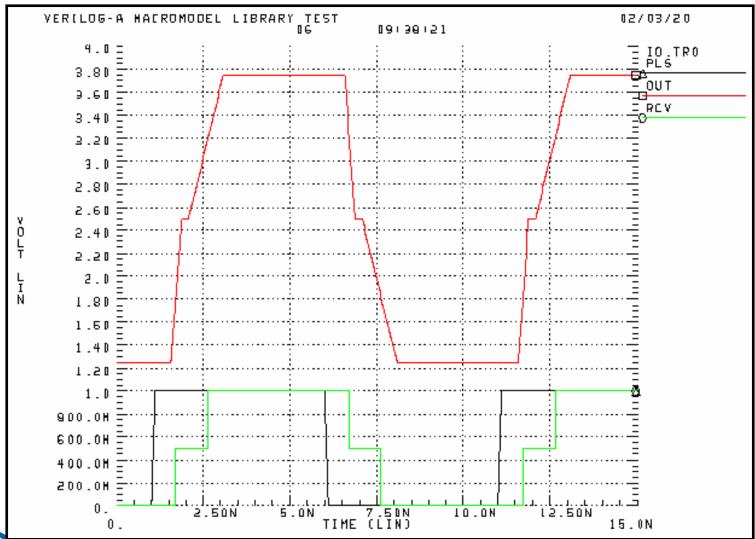

#### Verilog-A(MS) waveforms of IBIS\_IO

#### Parameter data file format

```

-- C comp parameters

C comp

5.00e-12

kC comp pc

0.25

kC_comp_pu

0.25

kC comp pd

0.25

kC comp qc

0.25

-- Vectors of the IV curve tables

Ipc data

0.08

0.00

0.00

0.00

Vpc data

-5.00

-1.00

5.00

10.00

Ipu data

0.10

VHDL-A(MS)

0.00

-0.10

-0.20

. . .

```

```

define IO data \

.C comp(5.0p), \

.kC_{comp_pc(0.25)},

.kC_comp_pu(0.25), \

.kC comp pd(0.25),

.kC\_comp\_gc(0.25), \

.IVpc length(4), \

. Ipc data(\{0.08, 0.00, 0.00, 0.00\}),

.Vpc data(\{-5.00, -1.00, 5.00, 10.00\}),

.IVpu length(4), \

.Ipu_data({ 0.10, 0.00, -0.10, -0.20}), \

.Vpu data(\{-5.00, 0.00, 5.00, 10.00\}),

.IVpd_length(4), \

.Ipd data(\{-0.10, 0.00, 0.10, 0.20\}),

.Vpd_data({-5.00, 0.00, 5.00, 10.00}), \

.IVgc length(4), \

.Igc data(\{-0.08, 0.00, 0.00, 0.00\}),

.Vgc data(\{-5.00, -1.00, 5.00, 10.00\}),

data({0.00, 0.50e-9, 0.80e-9, 3.00e-9})

```

#### Verilog-A(MS)

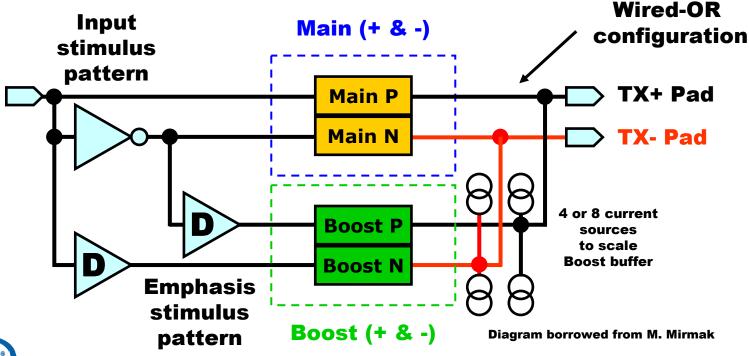

#### Pre-emphasis buffer - block diagram

- A differential pre/de-emphasis buffer

- a circuit netlist serves as the macro model, instantiating

- four Verilog-A or VHDL-AMS IBIS I/O buffer models,

- an inverter,

- two ideal delays, and

- eight current sources to scale the Boost buffer's current

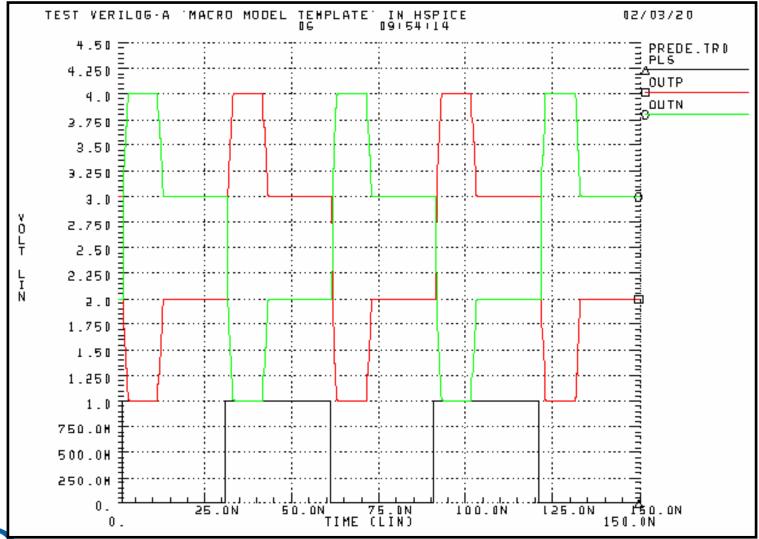

#### Pre-emphasis buffer - test bench

```

Test Verilog-A "Macro Model Template" in HSPICE

*****************

.TRAN 5.0ps 150.0ns

.OPTIONS POST=1 POST_VERSION=9007 PROBE

.hdl ".\PreDeMacro.va"

.PROBE TRAN

+ Pls = V(Pls)

+ OutP = V(Out_p)

+ OutN = V(Out n)

Vvcc Vcc 0 DC= 5.0

* This source represents a 111000111000 pattern

Pls 0 PULSE (1.0 0.0 1.0ns 1.0ps 1.0ps 30.0ns 60.0ns)

Pls Out_p Out_n Vcc Vcc 0

Vcc

PreDeMacro

In Out_p Out_n PC PU PD GC

Rld1 Out_p Vtt R= 50.0

Rld2 Out n Vtt R= 50.0

```

#### Pre-emphasis buffer - macro model

```

`include "constants.vams"

`include "disciplines.vams"

`include ".\AMS_files\IBIS_macro_library.va"

module PreDeMacro (InD, IOp, IOn, PCref, PUref, PDref, GCref, EnD);

input

InD, EnD;

electrical InD, EnD;

inout

IOp, IOn, PCref, PUref, PDref, GCref;

electrical IOp, IOn, PCref, PUref, PDref, GCref;

electrical InNM,

InPB,

InNB,

Dref;

electrical PUrefPB, PDrefPB, PCrefPB, GCrefPB;

electrical PUrefNB, PDrefNB, PCrefNB, GCrefNB;

electrical RcvPM,

RcvNM,

RcvPB,

RcvNB;

parameter real BitDelay = 10.0e-9;

parameter real ScaleBoost = -0.5;

`include "No_ODT_IO_data.dat"

IBIS_IO #(`IO_data) PosM (PUref, PDref, IOp, InD, EnD, RcvPM, PCref, GCref);

IBIS_IO #(`IO_data) NegM (PUref, PDref, IOn, InNM, EnD, RcvNM, PCref,

IBIS_IO #(`IO_data) PosB (PUrefPB, PDrefPB, IOP, InPB, EnD, RcvPB, PCrefPB, GCrefPB);

IBIS_IO #(`IO_data) NegB (PUrefNB, PDrefNB, IOn, InNB, EnD, RcvNB, PCrefNB, GCrefNB);

//- - - - - - - - - - PUref, PDref, IO, In, En, Rcv, PCref,

IBIS_V

#(.Vdc(1.0))

Dig1 (Dref, PDref);

IBIS VCVS

Inv1 (Dref, InNM, InD, PDref);

IBIS_VCVS_DELAY #(.TD(BitDelay)) Dly1 (InNB, PDref, InD, PDref);

IBIS_VCVS_DELAY #(.TD(BitDelay)) Dly2 (InPB, PDref, InNM, PDref);

IBIS CCCS #(.Scale(ScaleBoost)) IpcP (PCref, IOp, PCref, PCrefPB);

IBIS_CCCS #(.Scale(ScaleBoost)) IpuP (PUref, IOp, PUref, PUrefPB);

IBIS_CCCS #(.Scale(ScaleBoost)) IpdP (PDref, IOp, PDref, PDrefPB);

IBIS_CCCS #(.Scale(ScaleBoost)) IgcP (GCref, IOp, GCref, GCrefPB);

IBIS_CCCS #(.Scale(ScaleBoost)) IpcN (PCref, IOn, PCref, PCrefNB);

IBIS_CCCS #(.Scale(ScaleBoost)) IpuN (PUref, IOn, PUref, PUrefNB);

IBIS_CCCS #(.Scale(ScaleBoost)) IpdN (PDref, IOn, PDref, PDrefNB);

IBIS_CCCS #(.Scale(ScaleBoost)) IgcN (GCref, IOn, GCref, GCrefNB);

endmodule

```

#### **Pre-emphasis buffer - waveforms**

#### Wrap up

Links to the two test suites including the most current version of the macro model library

http://www.eda.org/pub/ibis/macromodel wip/Macro Lib VA HSPICE 2006 01 26.zip http://www.eda.org/pub/ibis/macromodel wip/Macro Lib VHDL SMASH 2006 02 01.zip

- Please try it out and provide feedback, that is the only way this effort can be made useful!

- Lots of capabilities and features could still be added to the library, but we need to know what is needed, and what is practical, etc...

- In case you need help to find SMASH...

http://www.dolphin-integration.com/medal/smash/smash\_download.html